Earlier this year, Intel announced the Falcon shores XPU product line. As a novel scalable chip design, it aims to use x86 and Xe cores to handle supercomputing workloads At the ISC 2022 Conference on Tuesday, Intel disclosed more configuration details of Falcon shores chip based on Xeon platform It can be seen that XPU architecture is not a simple CPU + GPU combination, but integrates several new technologies to make it stand out in several other fields.

At the first sight of XPU, many people may immediately associate that AMD has studied exascale APU for some time - the insight mi300 solution, which is expected to be launched sometime next year, combines Zen CPU core with cDNA chip.

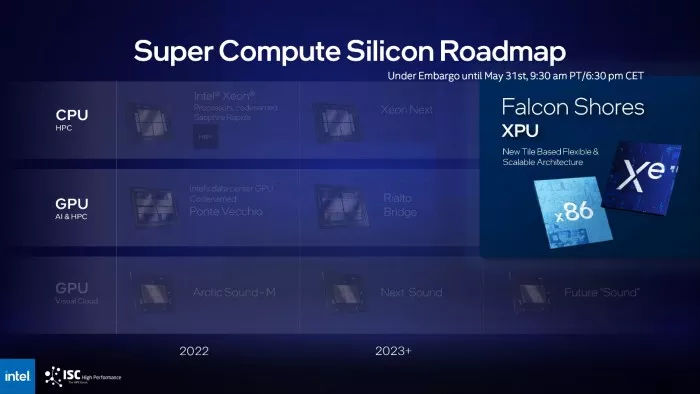

Looking ahead, Falcon shores is the next major architecture innovation in Intel's chip roadmap. It integrates x86 CPU and Xe GPU architecture into one slot.

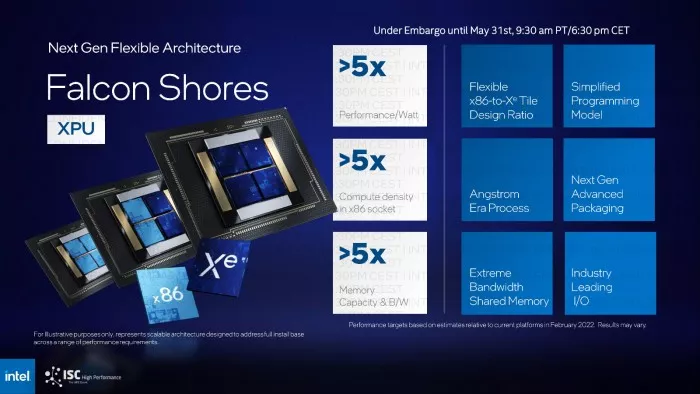

Intel hopes that by 2024, it will bring more than five times the performance power consumption ratio, computing density, storage capacity, bandwidth and other advantages.

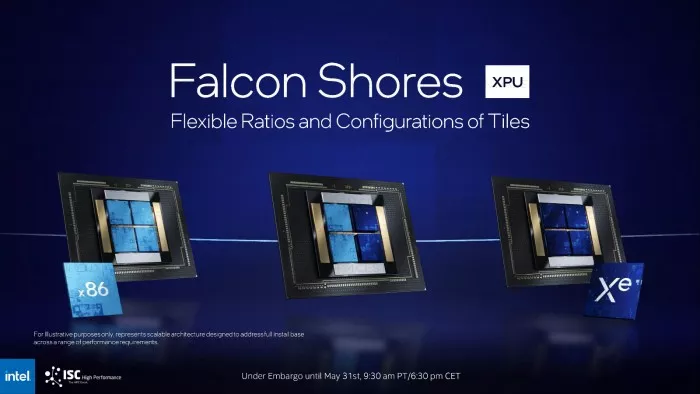

Intel also called Falcon shores XPU "a novel flexible and scalable architecture based on small tiles", which means that whether it is CPU, GPU or XPU, small tiles will become a basic part of Intel's next-generation chips.

The company presented three configurations at ISC 2022 Conference (for illustration purposes only), including a complete set of X86 tiles, a set of Xe GPU tiles, and a solution using x86 CPU + Xe GPU kernel at the same time.

The emphasis of the three configurations is different, but the common point of all designs is that they have at least four tiles - the layout is similar to Intel's Sapphire rapids Xeon CPU product line.

Although Intel has not mentioned a solution based on high bandwidth cache (HBM), we do not rule out the possibility of subsequent upgrade models.

Here are some highlights of Falcon shores XPU:

● flexible x86 and Xe tile design ratio

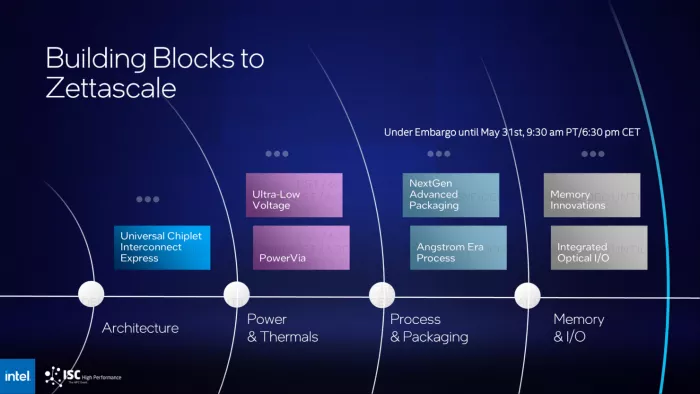

● progress towards angstrom level process

● ultra high shared cache bandwidth

● simplified programming model

● next generation advanced packaging technology

● industry leading i/o

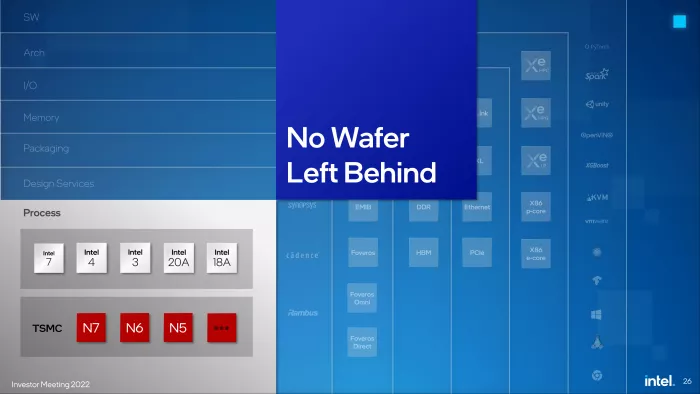

Since Intel has mentioned "angstrom" (1a = 0.1nm) level process nodes, we speculate that Falcon shores XPU is based on 20A or 18a process.

According to Intel's Roadmap, this XPU is expected to be launched around 2024-2025, and the company may provide the option of HBM based high bandwidth cache.

In addition, compared with the standard single chip design, Falcon shores XPU will use more complex next-generation advanced packaging (such as the iterative version of emib / foveros).

The preliminary performance advantages of the Falcon shores XPU design shared by Intel are as follows:

● more than 5 times per watt characteristics can be improved

● increase the computing density of X86 slots by more than 5 times

● provide more than five times of memory capacity / bandwidth support

It should be noted that the above performance targets are only estimated for the existing platforms in february2022.

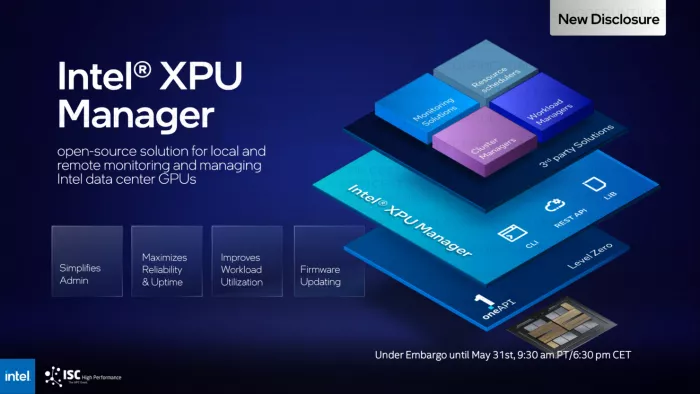

In addition, the entire Intel Falcon shores XPU platform will be adjusted around the oneapi software suite to provide open source solutions for local / remote monitoring and management of data center level chips.

Finally, given that Falcon shores XPU product line is still in the early development stage, it is obvious that the company will disclose more details in the upcoming activities.