Today, it is integrated into the code of mainline llvm 15.0 and adds "ampere1" support of ampere computing to the clang compiler This is their next-generation server processor, which adopts the internal "ampere cores" kernel design.

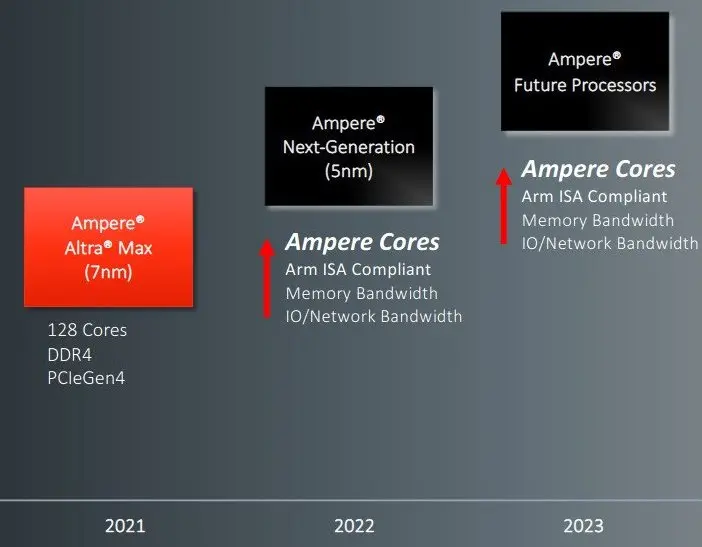

Ampere's current generation of ampere Altra and ampere Altra Max processors are already very competitive, with up to 128 physical cores per socket and an arm neoverse-n1 7 nm design. However, as pointed out last year, ampere has begun to study their own core design, which is expected to be launched later in 2022.

Last year, ampere next generation was confirmed to be based on 5 nm, with arm isa compliant design and next-generation memory (ddr5) and storage capacity. However, the details of this ampere Altra / Altra Max successor are still few and will usher in their own core design. The 2022 design code of ampere is also known as siryn.

Included in the llvm is "ampere1". Initial compiler support for the "ampere1" target has been added and complies with armv 8.0 6-A ISA。 This at least confirms armv8 6-A was used in this original internal ampere core design, not armv9, but armv8 with neoverse N1 core Compared with 2, it has been significantly improved.

Ampere1 compiler target confirms armv8 6-A with fp16 and MTE (memory label) extensions, and enable speculative barrier (sb) and speculative storage bypass security (SSBs) options. This llvm support patch is ampere-1 support added to the gcc compiler in November.