Amd said at the recent investor earnings conference call that it plans to implant the newly acquired FPGA AI reasoning engine of Xilinx company into the future epyc processor The first batch of new products is expected to come out in 2023, which shows how eager AMD is to make this $54 billion deal profitable to meet future demand and bring significant growth.

Since the acquisition, we have seen many patent documents, indicating that AMD is seeking to enable AI accelerator in its processor product lineup through a variety of designs, and apply a loose 3D chip stacking technology based on competitive designs.

As a reference, Intel spent $16.7 billion to acquire Altera in the second half of 2015, and then quickly started the CPU / FPGA integration design based on Altera chip technology. However, the experimental products are not only delayed to 2018, but also limited in design.

Since then, Intel's strategy has become a little vague* Even so, Victor Peng, President of AMD's adaptive and embedded computing division, commented on the conference call * - Xilinx once carried out image recognition with the help of AI engine.

Its latest trends include building other reasoning applications on AMD's current embedded software and edge products (such as vehicle platform). What amd values most is the flexible adjustment and adaptability of its structure technology.

AMD is committed to developing unified global software and supports a wide product portfolio, especially AI based reasoning and computing. Interested friends can pay attention to more details shared by the company during the financial analyst day (June 9, 2022).

Although officials are tight lipped about the future planning of new products based on FPGA, it is generally expected that the new chip will integrate many advanced technologies - such as supporting the new generation PCIe standard and improving the QPI interconnection compatibility between CPU and FPGA chipset.

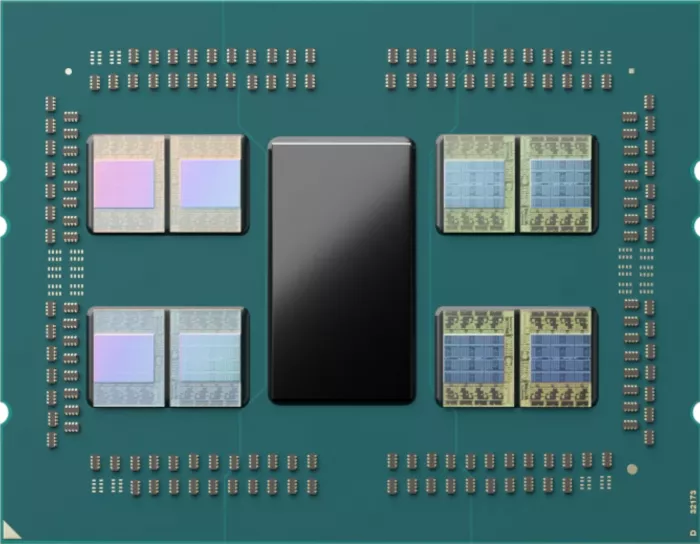

In addition, AMD is expected to improve the consistency across a variety of equipment and technical solutions through novel accelerator ports. In the 3D stacking scheme, a small FPGA chip can be placed on the top of the I / O chip of the CPU, and the process can refer to the milan-x server processor.

However, while improving memory throughput and chip performance, 3D stacking may also lead to embarrassing heat accumulation problems. If the FPGA chip is too close to the I / O die, the heat emitted by the CPU under high load may also affect it and degrade its performance.

Incidentally, amd recently disclosed the epyc Bergamo chip. It can be seen that this series of CPUs adopts a new Zen 4C core (up to 128C / 256t), which is particularly efficient in programming and cloud scenarios.

Through the accelerator port in AMD CPU design, the company can also flexibly use other accelerators in its design (such as ASIC, DSP and GPU), which means that customers such as data center can easily choose the customization options that best meet their needs.

Finally, Dr. Lisa Su, amd CEO, said: "we now have an industry-leading portfolio of high-performance and adaptive computing engines, and foresee more opportunities to use these extended technology portfolios to provide a stronger portfolio.".